| Das eBook Angewandte Mikroelektronik wurde von Hans Lohninger zur Unterstützung verschiedener Lehrveranstaltungen geschrieben. Weitere Informationen finden sie hier. |

|

Home  Digitaltechnik Digitaltechnik  Flip-Flop Flip-Flop |

||||||||||||||||||||||||||||||

| Siehe auch: Zähler, Experiment: Einsatz eines Registers zur Datenspeicherung, Experiment: Aufbau eines RS-Flip-Flops aus NAND-Gattern | ||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||

Flip-Flop

Verschaltet man zwei NAND-Gatter in der in Abbildung dargestellten Form, so erhält man die einfachste Form eines Flip-Flops. Ein Flip-Flop ist eine Schaltung, die zwei stabile Zustände kennt und die durch Anlegen eines Signals von außen vom einen in den anderen Zustand geschaltet werden kann. Ein Flip-Flop kann also Information (1 Bit) speichern.

Für das oben dargestellte Flip-Flop sei, um seine Funktion zu verstehen, die Wahrheitstafel betrachtet:

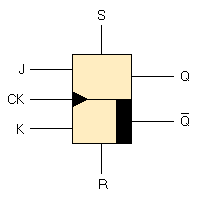

Das RS-Flip-Flop hat jedoch einen entscheidenden Nachteil: Es behält seinen Zustand nur bis zum nächsten Puls an einem der Eingänge bei. Diese Eigenschaft ist oft unerwünscht, da man beliebige Eingangszustände zu definierten Zeitpunkten übernehmen möchte (zwischendurch muss sich das Eingangssignal ändern dürfen, ohne den Ausgang zu beeinflussen). Dieser Nachteil wird durch das JK-Flip-Flop behoben. Das JK-Flip-Flop verfügt neben den Dateneingängen (J,K) auch noch über einen Takteingang (CK) und meist auch über Set- und Reset-Eingänge (R,S). Die Ausgänge Q und /Q übernehmen den Eingangszustand nun nur mehr bei Erscheinen eines Taktimpulses. Dazwischen kann sich der Eingang beliebig ändern, ohne den Ausgang zu beeinflussen. Ein JK-Flip-Flop wird durch folgendes Schaltbild dargestellt:

Eine etwas veränderte, jedoch sehr häufige Spielart eines JK-Flip-Flops ist das D-Flip-Flop. Bei diesem Flip-Flop sind die Eingänge J & K mit einem Inverter verbunden und als ein Eingang (D) herausgeführt:

Am Eingang D kann entweder 0 oder 1 anliegen; der jeweilige Zustand wird durch einen Impuls an CK in den Ausgang übernommen. Man kann mehrere D-Flip-Flops parallel schalten und erhält damit ein n Bit breites Register (latch), das die Information am Eingang beim Auftreten eines Taktimpulses in den Ausgang übernimmt:

|

||||||||||||||||||||||||||||||

Home  Digitaltechnik Digitaltechnik  Flip-Flop Flip-Flop |

||||||||||||||||||||||||||||||

Last Update: 2008-05-31